江蘇入門級FPGA開發板工程師

1.FPGA開發板的時鐘模塊作用時鐘信號是FPGA數字邏輯設計的“脈搏”,開發板上的時鐘模塊通常由晶體振蕩器、時鐘緩沖器和時鐘分配網絡組成。晶體振蕩器能提供高精度的固定頻率信號,常見頻率有25MHz、50MHz、100MHz等,部分板卡還會集成可配置的時鐘發生器,支持通過軟件調整輸出頻率,滿足不同算法對時鐘周期的需求。時鐘緩沖器可將單一時鐘信號復制為多路同步信號,分配給FPGA內部的不同邏輯模塊,避免因信號延遲導致的時序偏差。在高速數據處理場景中,如圖像處理或通信信號解調,時鐘模塊的穩定性直接影響數據采樣精度和邏輯運算的同步性,因此部分開發板還會加入時鐘抖動抑制電路,進一步降低信號噪聲。FPGA 開發板硬件資源配置可軟件查詢。江蘇入門級FPGA開發板工程師

FPGA開發板在能源管理系統中的應用有助于提高能源利用效率。在智能電網領域,開發板可通過連接各類電力傳感器,實時采集電網中的電壓、電流、功率等參數。對采集到的數據進行分析處理,監測電網的運行狀態,判斷電網是否處于正常工作范圍。當檢測到電網出現異常情況,如電壓波動過大、功率失衡等,開發板可及時發出預警信息,并將數據上傳至電網管理中心,為管理人員進行決策提供依據。在可再生能源發電系統中,如太陽能發電、風力發電等,開發板可用于發電設備的運行。根據環境條件,如光照強度、風速等,調節發電設備的工作參數,實現最大功率點,提高能源轉換效率。同時,開發板還可以對發電系統的電能質量進行監測與優化,確保發電系統穩定可靠地向電網供電,促進能源行業的可持續發展。江蘇國產FPGA開發板入門FPGA 開發板接口間距符合標準封裝尺寸。

按鈕是FPGA開發板上常見的輸入外設,通常為輕觸式按鍵,數量從2個到8個不等,用于實現人機交互和邏輯控制。按鈕的功能是輸入觸發信號,開發者可通過檢測按鈕的按下與釋放動作,控制FPGA內部邏輯的啟動、停止或參數調整。例如,在計數器實驗中,可通過按下按鈕啟動計數,再次按下停止計數;在狀態機實驗中,可通過不同按鈕切換狀態機的運行模式。由于機械按鈕存在抖動現象,按下或釋放瞬間會產生多次電平跳變,FPGA需通過軟件消抖或硬件消抖電路處理,確保檢測到穩定的電平信號。部分開發板會集成硬件消抖電路,簡化軟件設計;也有開發板通過電容濾波或RC電路實現消抖,降低成本。在實際應用中,按鈕常與LED、數碼管等外設配合使用,實現直觀的交互功能。

UART 接口是 FPGA 開發板與計算機或其他設備進行串行通信的常用接口,通常由 TX(發送端)和 RX(接收端)兩根信號線組成,支持異步通信模式。在開發過程中,UART 接口可用于數據交互,例如將 FPGA 內部的運算結果發送到計算機串口助手顯示,或接收計算機發送的控制指令,調整 FPGA 的邏輯功能。部分開發板會集成 USB 轉 UART 芯片,將 UART 信號轉換為 USB 信號,直接與計算機 USB 端口連接,無需額外的串口適配器。在嵌入式系統開發中,UART 接口還可用于調試信息輸出,開發者通過查看串口打印的日志,快速定位程序運行中的問題,例如變量數值異常或邏輯分支錯誤。FPGA 開發板時鐘選擇電路支持頻率切換。

FPGA開發板的離線運行是指不依賴計算機,通過外部存儲設備(如SPIFlash、SD卡)加載配置文件和應用程序,適合嵌入式系統和現場應用場景。離線運行設計需滿足兩個**需求:一是配置文件的自動加載,二是應用程序執行。配置文件自動加載可通過FPGA的上電配置功能實現,將編譯后的.bit文件存儲到SPIFlash中,FPGA上電后自動從Flash讀取配置文件,完成初始化;部分開發板支持多配置文件存儲,可通過板載按鍵或外部信號選擇加載的配置文件。應用程序**執行需FPGA實現完整的功能邏輯,包括外設控制、數據處理和交互功能,例如設計一個離線數據采集系統,FPGA從傳感器采集數據,存儲到SD卡,通過LED顯示工作狀態,無需計算機干預。離線運行還需考慮系統穩定性,例如加入watchdog(看門狗)電路,當系統出現死機時自動重啟;加入電源管理模塊,支持低功耗模式,延長電池供電時間。 FPGA 開發板教程覆蓋從基礎到進階內容。江蘇國產FPGA開發板入門

FPGA 開發板示例代碼提供設計模板參考。江蘇入門級FPGA開發板工程師

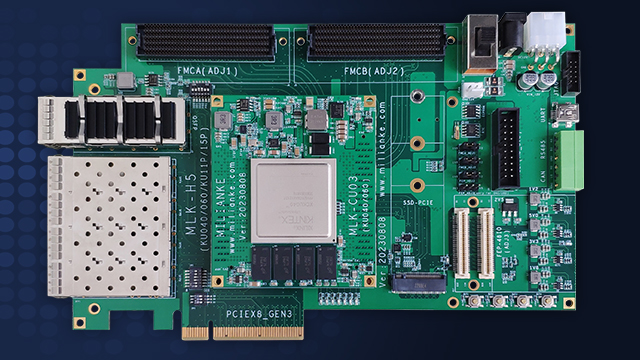

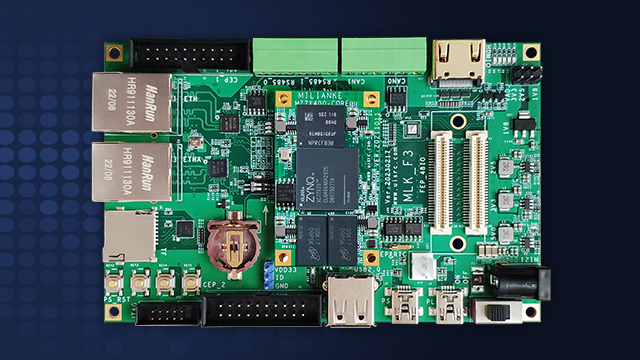

FPGA芯片的邏輯資源是衡量開發板性能的重要指標,包括邏輯單元(LE)、查找表(LUT)、觸發器(FF)、DSP切片和塊RAM(BRAM)等,選型時需根據項目需求匹配資源規模。對于入門級項目,如基礎邏輯實驗、簡單控制器設計,選擇邏輯單元數量在1萬-10萬之間的FPGA芯片即可,如XilinxArtix-7系列的xc7a35t芯片,具備35k邏輯單元、50個DSP切片和900KBBRAM,能滿足基礎開發需求。對于要求高的項目,如AI推理加速、高速數據處理,需選擇邏輯單元數量在10萬-100萬之間的芯片,如XilinxKintex-7系列的xc7k325t芯片,具備326k邏輯單元、1728個DSP切片和BRAM,支持復雜算法的實現。DSP切片數量影響信號處理能力,適合需要大量乘法累加運算的場景;塊RAM容量影響數據緩存能力,適合需要存儲大量中間數據的項目。選型時需避免資源過剩導致成本浪費,也需防止資源不足無法實現設計功能,可通過前期需求分析和資源估算確定合適的芯片型號。 江蘇入門級FPGA開發板工程師

- 河南安路FPGA開發板加速卡 2025-12-19

- 浙江FPGA套件 2025-12-19

- 江蘇入門級FPGA開發板工程師 2025-12-19

- 廣東使用FPGA開發板套件 2025-12-19

- 黑龍江工控板FPGA開發板套件 2025-12-19

- 天津賽靈思FPGA開發板平臺 2025-12-19

- XilinxFPGA開發板基礎 2025-12-19

- 浙江安路開發板FPGA開發板定制 2025-12-19

- 北京工控板FPGA開發板加速卡 2025-12-19

- 天津核心板FPGA開發板加速卡 2025-12-19

- 黃浦區新型工控機哪家好 2025-12-19

- 內蒙古插座SIM卡座廠家 2025-12-19

- 青浦區質量二極管設計 2025-12-19

- 北京MCU微控制器電子元器件咨詢 2025-12-19

- 本地整流器廠家電話 2025-12-19

- 太原多路并行微型模塊3.125G 2025-12-19

- 汕頭高性能自恢復保險絲供應商 2025-12-19

- 江蘇高精度IMU傳感器生產廠家 2025-12-19

- 無源通信防偽標簽選哪家 2025-12-19

- 姑蘇區優勢MPCB鋁基板電話多少 2025-12-19