上海國產芯片封裝廠家

芯片封裝在人工智能領域的應用:人工智能芯片對算力、能效比有極高要求,這對芯片封裝技術提出了更高挑戰。中清航科針對人工智能芯片的特點,采用先進的3D封裝、SiP等技術,提高芯片的集成度和算力,同時優化散熱設計,降低功耗。公司為人工智能領域客戶提供的封裝解決方案,已成功應用于深度學習服務器、智能安防設備等產品中,助力人工智能技術的快速發展和應用落地。想要了解更多內容可以關注我司官網,同時歡迎新老客戶來電咨詢。芯片封裝考驗細節把控,中清航科以嚴苛標準,確保每顆芯片穩定運行。上海國產芯片封裝廠家

隨著摩爾定律逼近物理極限,先進封裝成為提升芯片性能的關鍵路徑。中清航科在Fan-Out晶圓級封裝(FOWLP)領域實現突破,通過重構晶圓級互連架構,使I/O密度提升40%,助力5G射頻模塊厚度縮減至0.3mm。其開發的激光解鍵合技術將良率穩定在99.2%以上,為毫米波通信設備提供可靠封裝方案。面對異構集成需求激增,中清航科推出3DSiP立體封裝平臺。該方案采用TSV硅通孔技術與微凸點鍵合工藝,實現CPU、HBM內存及AI加速器的垂直堆疊。在數據中心GPU領域,其散熱增強型封裝結構使熱阻降低35%,功率密度提升至8W/mm2,滿足超算芯片的嚴苛要求。半導體封裝外殼企業5G 芯片對封裝要求高,中清航科定制方案,適配高速傳輸場景需求。

中清航科在芯片封裝領域的優勢-技術實力:中清航科擁有一支由專業技術人才組成的團隊,他們在芯片封裝技術研發方面經驗豐富,對各類先進封裝技術有著深入理解和掌握。公司配備了先進的研發設備和實驗室,持續投入大量資源進行技術創新,確保在芯片封裝技術上始終保持帶頭地位,能夠為客戶提供前沿、質優的封裝技術解決方案。中清航科在芯片封裝領域的優勢-設備與工藝:中清航科引進了國際先進的芯片封裝設備,構建了完善且高效的生產工藝體系。從芯片的預處理到封裝完成,每一個環節都嚴格遵循國際標準和規范進行操作。通過先進的設備和優化的工藝,公司能夠實現高精度、高可靠性的芯片封裝,有效提高產品質量和生產效率,滿足客戶大規模、高質量的訂單需求。

面對衛星載荷嚴苛的空間環境,中清航科開發陶瓷多層共燒(LTCC)MCM封裝技術。采用鎢銅熱沉基底與金錫共晶焊接,實現-196℃~+150℃極端溫變下熱失配率<3ppm/℃。通過嵌入式微帶線設計將信號串擾抑制在-60dB以下,使星載處理器在單粒子翻轉(SEU)事件率降低至1E-11errors/bit-day。該方案已通過ECSS-Q-ST-60-13C宇航標準認證,成功應用于低軌衛星星務計算機,模塊失效率<50FIT(10億小時運行故障率)。針對萬米級深海探測裝備的100MPa超高壓環境,中清航科金屬-陶瓷復合封裝結構。采用氧化鋯增韌氧化鋁(ZTA)陶瓷環與鈦合金殼體真空釬焊,實現漏率<1×10?1?Pa·m3/s的密封。內部壓力補償系統使腔體形變<0.05%,保障MEMS傳感器在110MPa壓力下精度保持±0.1%FS。耐腐蝕鍍層通過3000小時鹽霧試驗,已用于全海深聲吶陣列封裝,在馬里亞納海溝實現連續500小時無故障探測。中清航科聚焦芯片封裝創新,用模塊化設計滿足多樣化應用需求。

中清航科部署封裝數字孿生系統,通過AI視覺檢測實現微米級缺陷捕捉。在BGA植球工藝中,球徑一致性控制±3μm,位置精度±5μm。智能校準系統使設備換線時間縮短至15分鐘,產能利用率提升至90%。針對HBM內存堆疊需求,中清航科開發超薄芯片處理工藝。通過臨時鍵合/解鍵合技術實現50μm超薄DRAM晶圓加工,4層堆疊厚度400μm。其TSV深寬比達10:1,阻抗控制在30mΩ以下,滿足GDDR6X1TB/s帶寬要求。中清航科可拉伸封裝技術攻克可穿戴設備難題。采用蛇形銅導線與彈性體基底結合,使LED陣列在100%拉伸形變下保持導電功能。醫療級生物相容材料通過ISO10993認證,已用于動態心電圖貼片量產。量子芯片封裝要求極高,中清航科低溫封裝技術,助力量子態穩定保持。浙江國內cob封裝廠家

中清航科聚焦芯片封裝,用仿真預判風險,縮短研發驗證周期。上海國產芯片封裝廠家

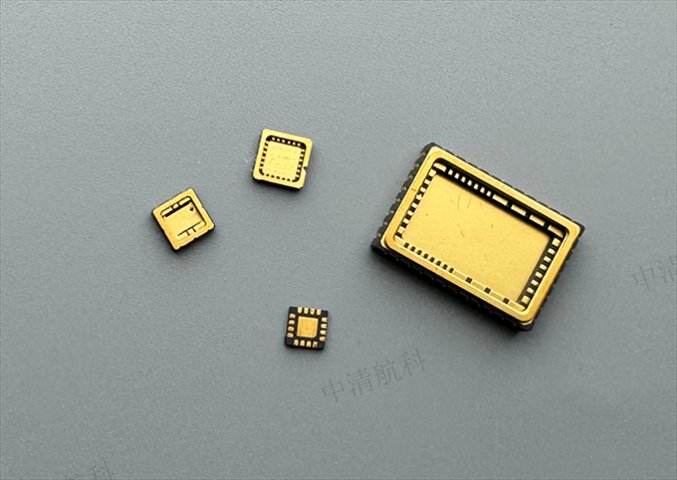

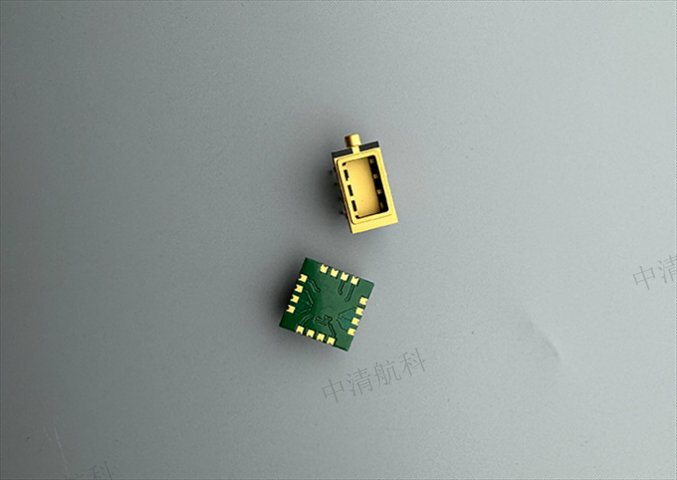

芯片封裝的基礎概念:芯片封裝,簡單來說,是安裝半導體集成電路芯片的外殼。它承擔著安放、固定、密封芯片的重任,能有效保護芯片免受物理損傷以及空氣中雜質的腐蝕。同時,芯片封裝也是溝通芯片內部與外部電路的關鍵橋梁,芯片上的接點通過導線連接到封裝外殼的引腳上,進而與印制板上的其他器件建立連接。中清航科深諳芯片封裝的基礎原理,憑借專業的技術團隊,能為客戶解讀芯片封裝在整個半導體產業鏈中的基礎地位與關鍵作用,助力客戶從源頭理解相關業務。上海國產芯片封裝廠家

- 芯片堆疊封裝 2025-12-23

- 上海國產芯片封裝廠家 2025-12-23

- 上海傳感器封裝 2025-12-23

- 金屬陶瓷封裝 2025-12-23

- 上海mems晶圓級真空封裝 2025-12-23

- 江蘇wlcsp封裝焊接方法 2025-12-23

- 江蘇集成電路to封裝 2025-12-23

- 上海sip 封裝代工廠 2025-12-23

- 浙江倒裝cob封裝 2025-12-23

- 江蘇to-252 封裝 2025-12-23

- 青浦區打印紙型號 2025-12-23

- 湖南電腦端數字化移交平臺哪些好用 2025-12-23

- 張家港通用LCD顯示器比較 2025-12-23

- 廣東機架式服務器一般多少錢 2025-12-23

- 10卡服務器系統 2025-12-23

- 崇明區訂單管理系統開發應用范圍 2025-12-23

- 南昌clou超高頻讀寫器芯片 2025-12-23

- 深圳結構定制定制化服務 2025-12-23

- 吳中區質量CRT顯示器推薦廠家 2025-12-23

- 初中物理教師備課軟件下載 2025-12-23